# **Science Discovery**

2020; 8(4): 74-78

http://www.sciencepublishinggroup.com/j/sd

doi: 10.11648/j.sd.20200804.13

ISSN: 2331-0642 (Print); ISSN: 2331-0650 (Online)

# A FPGA Serial Port Transmission Fault Analysis and Design Optimization

Shen Xiaohe\*, Niu Jing, Hu Xiaoxi

Beijing Institute of Aerospace Control Devices, Beijing, China

#### **Email address:**

shenxiaohe2008@163.com (Shen Xiaohe), ruomuzi608@163.com (Niu Jing), Huxx615@126.com (Hu Xiaoxi)

\*Corresponding author

#### To cite this article:

Shen Xiaohe, Niu Jing, Hu Xiaoxi. A FPGA Serial Port Transmission Fault Analysis and Design Optimization. *Science Discovery*. Vol. 8, No. 4, 2020, pp. 74-78. doi: 10.11648/j.sd.20200804.13

Received: June 21, 2020; Accepted: August 18, 2020; Published: August 25, 2020

**Abstract:** One of the functions of FPGA in a satellite equipment is to receive data framing instructions from main control system, solve the data of the sensor at this time, and send the data through the serial port according to the format of response frame. In the system joint debugging, a small amount of data sent by serial port are not collected correctly by the receiving equipment, and the fault happened by accident. This paper analyzes the reason of this fault and puts forward an effective solution to this problem. First of all, this paper analyzes the principle of serial port transmitting function and the fault phenomenon. It is found that the failure function is the FPGA serial port transmitting. Then, the serial transmission function of FPGA is further decomposed to list all possible cases, and the fault is reproduced in the function simulation by using Questa Sim. This paper carefully analyzes the mechanism of this failure and the probability of this failure. Finally, this paper proposed a solution, which is proved to be effective by experiments. This paper gives corresponding suggestions from three aspects of software design, engineering implementation and system testing. This has reference significance for the future engineering application.

**Keywords:** Serial Port Transmission, FPGA, Fault Analysis, State Machine

# 一种FPGA串口发送故障分析及设计优化

# 申小禾\*, 牛静, 胡晓曦

北京航天控制仪器研究所, 北京, 中国

#### 邮箱

shenxiaohe2008@163.com (申小禾), ruomuzi608@163.com (牛静), Huxx615@126.com (胡晓曦)

摘要:某星载设备中FPGA的一个功能是接收数据组帧指令,解算传感器的数据,并将数据按照应答帧格式组帧通过串口发送。在系统联调中,出现少量FPGA串口发送的数据未被接收设备正确采集的故障,且故障具有偶发性。本文针对这一故障进行分析并提出解决方案。首先分析串口发送原理及实验现象,定位出现故障的范围为FPGA串口发送功能;然后对FPGA的串口发送功能进一步分解,列出所有可能的情况,在仿真情况下重现了故障;接着分析了故障出现的机理,以及出现的概率;最后提出了一种解决方案,并通过了试验验证了其有效性。本文分别从软件设计、工程实现和系统测试方面给出相应的建议,这对以后的工程应用具有借鉴意义。

关键词: 串口发送, FPGA, 故障分析, 状态机

# 1. 引言

某星载设备中FPGA的主要功能是接收外部温度传感器等产品目前环境信息,当地面设备向FPGA发送数据组帧指令后,FPGA解析组帧指令,统计并计算产品的环境信息,然后将其按照通讯协议格式组帧,通过RS422串口发送给地面设备。帧头、帧尾、校验位正确的串口数据才能被地面的接收设备正确接收,FPGA发送串口的波特率为115.2bps,帧头为0xAA、0x55,中间是数据位,帧尾为校验和。在系统联调阶段出现接收设备接收的串口数据丢帧的情况。通过示波器采集FPGA串口信号,在接收设备未收到FPGA发送的串口数据时,FPGA发送的数据帧正确,即帧头、数据位、校验都正确,但是帧头0xAA的起始位只保持了4400ns,约为完整发送一位的一半(正常时间应为8680ns)。每次串口接收异常时,都是帧头0xAA的起始位只有半位,数据帧中的其他数据未出现此问题。

由于串口发送的所有功能由FPGA完成,初步断定这个故障是FPGA软件设计的缺陷导致的[1]-[3]。因此先对FPGA串口发送功能进行分解,经分析确定此故障是FPGA中串口发送状态机的设计缺陷导致,针对此设计缺陷提出了解决方案,经过功能仿真和实物验证,此方法有效的修正了故障。由此提出FPGA串口发送状态机设计的建议,以及FPGA测试的建议。

# 2. 串口发送功能分解

串口发送功能的实现分两部分: 波特率生成和串口数据发送[4-5]。波特率生成即产生设定的波特率时钟使能,使数据按照设定的波特率发送。串口数据发送使用状态机实现,控制串口数据发送的顺序[6-7]。因为是FPGA串口发送异常,所以将故障的原因锁定在波特率产生和串口数据发送这两部分,下面对这两个功能的实现进行分解。

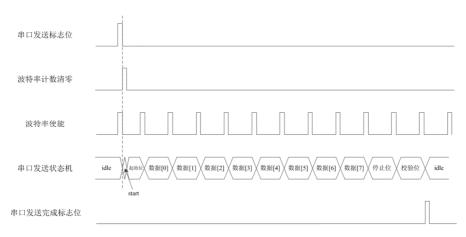

#### 2.1. 波特率生成功能

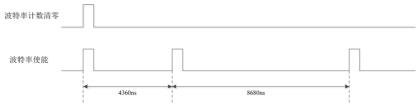

波特率生成功能由FPGA的全局时钟计数实现,生成波特率使能,通过使能信号控制串口输出数据的跳变。FPGA全局时钟频率为25MHz,25MHz/115.2kbps≈217,即每计数217次输出波特率使能信号。

在复位时波特率计数寄存器S\_counter\_nco置0,复位结束后,S\_counter\_nco开始计数,波特率计数器每次累加 0x12E , 当 S\_counter\_nco[15]=1 且 时 波 特 率 时 钟 S\_baud\_clk=0'时输出波特率使能S\_clk\_1x\_pa的高电平脉冲,波特率计数寄存器S\_counter\_nco清零后第一次累计 109 次 S\_counter\_nco[15]=1 , 之 后 每 累 计 217 次 S\_counter\_nco[15]=1。波特率计数寄存器清零后第一个波特率使能出现在4360ns(109 $\times$ 40=4360ns)处,之后每隔 8680ns(217 $\times$ 40=8680ns)出现,当波特率计数清零时,重新计数。波特率使能信号时序图如图1所示。

图1 波特率使能信号时序图。

#### 2.2. 串口数据发送功能

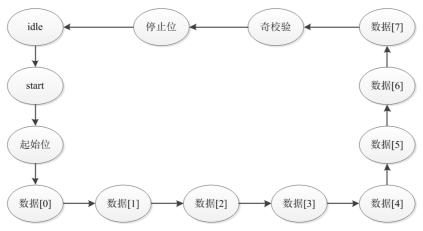

串口发送格式依次为1位起始位,8位数据位,1位奇校验位,1位停止位,起始位低有效,停止位高有效,数

据位由低到高发送,波特率为115.2kbps。在FPGA软件中串口数据发送功能由状态机counter实现,在数据就绪后开始发送数据,状态迁移图如图2所示。

图2 状态迁移图。

状态机中无可不到达或无法跳出的状态。故障现象显示,发生故障的状态为"起始位",所以重点由"起始位"状态前后的状态跳转,同时分析其他状态的跳转,分析为什么只在第一个帧头的起始位出现故障。

#### (1) "idle"→"start"

当I\_rfd='1'且S\_sdo\_done='0'时,状态由"idle"跳转到 "start",同时波特率计数清零。

I\_rfd为串口发送标志位,当接收到数据组帧发送指令时,FPGA完成串口发送数据的组帧,当数据帧中需发送的串口数据准备好后,I\_rfd为高电平脉冲,其余时为低电平。

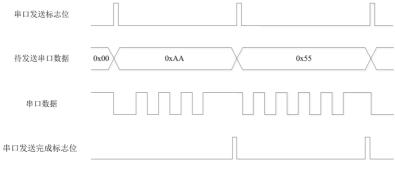

S\_sdo\_done为串口发送完成标志位,当完成发送一个数据时输出高电平脉冲,其余时为低电平,其波形如图3所示。串口发送标志位和串口发送完成标志位的时序图见图3。

图3 串口发送时序图。

#### (2) "start"→"起始位"

在"start"状态,当波特率使能S\_clk\_1x\_pa为高电平时,进入"起始位"状态。原设计中波特率时钟在复位开始产生,每当收到波特率计数后更新,以保证每次数据发送时的波特率准确。

# (3) "起始位"→"数据[0]"

在"起始位"状态,当波特率使能为高电平时,进入"数据[0]"状态。与"start"跳转到"起始位"的条件一致,使用相同的语句分支。

#### (4) 其他状态跳转

在发送数据位、校验位的状态时,每当波特率使能为 高电平时,进入下一个状态。在"停止位"状态,当波特率 使能为高电平时,进入"idle"状态,同时串口发送完成标志位输出高脉冲。

#### 3. 故障分析

#### 3.1. 故障定位

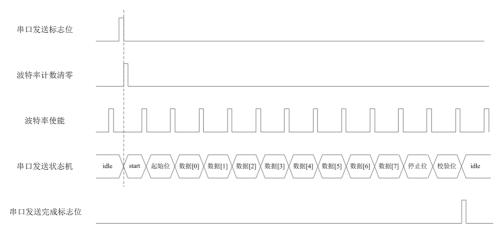

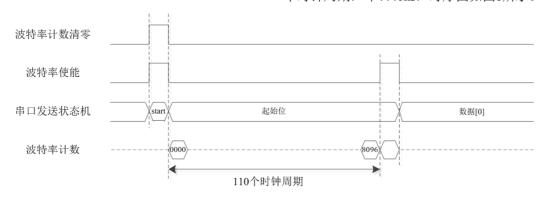

通常情况下,串口发送标志位I\_rfd出现高电平脉冲时,波特率计数清零,4360ns后波特率使能输出高脉冲(见图4),进入"起始位"状态,之后每隔8680ns输出波特率使能高脉冲,直到一个数据发送完成。

图4 正常情况时序图。

只看波特率生成功能或串口数据发送功能,在功能实现上没有问题,所以重点关注两个功能间相关联的信号,即串口发送标志位I\_rfd和波特率使能S\_clk\_lx\_pa。串口发送标志位I\_rfd与接收到地面设备的数据组帧指令有关,当串口发送标志位出现高脉冲时表示开始输出串口数据,同时对波特率计数寄存器S counter nco清零。波特率使能

S\_clk\_1x\_pa的时序受波特率计数寄存器S\_counter\_nco的影响。当"idle"跳转到"start"时,波特率计数清零,如果此时波特率时钟S\_clk\_1x\_pa刚好为'l',状态机立即进入"起始位"状态,在清零后第一次波特率使能为高脉冲时进入下一状态,导致在"起始位"状态只保持半位的时间,所以起始位只有一半(见图5)。

图5 异常情况时序图。

在发送完0xAA后,S\_clk\_1x\_pa使能有效,串口发送状态机由"停止位"跳转到"idle",在"idle"时对rd\_en置位,所以在发送除0xAA外的其他数据时,不会出现刚跳转到"start"状态下S\_clk\_1x\_pa刚好为1的情况,所以在发送其他数据时不会出现发送帧头0xAA的状况。

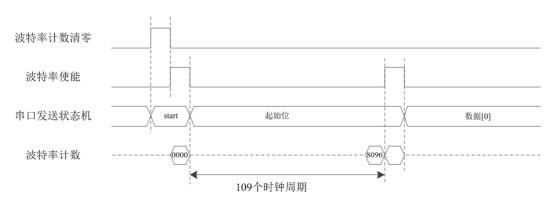

# 3.2. 故障情况分类

经过分析,故障有两种情况,一种情况波特率计数清 零与波特率使能的高电平重合,这种情况起始位持续111 个时钟周期,即4440ns,时序图如图6所示。

图6 第1种故障模型时序图。

另一种情况波特率使能高电比与波特率使能高电平延迟1个时钟,起始位持续110个时钟周期,即4400ns,时序图如图7所示。

图7 第2种故障模型时序图。

#### 3.3. 故障概率分析

波特率时钟S\_clk\_1x\_pa的时序是固定的,I\_rfd为高电平的时刻与接收到外部数据组帧发送指令RX的时刻有关。

经过功能仿真,发现在每8680ns内RX在其中80ns会出现这种异常情况,概率为0.92%,与系统调试时出现故障的概率相近。故障概率示意图见图8。

图8 故障概率示意图。

# 3.4. 故障解释

这次发生的故障在系统调试时出现,在单机测试时未发现,因为单机测试和系统联调时的串口接收设备接收机制不同有关[8-[9]。单机测试时的串口接收设备在检测到信号后按波特率时间间隔采数,所以未发现错误;而系统联调时的串口接收设备在串口信号每一位的中间位置采集数据,导致出现不能接收异常数据。

# 4. 设计优化及建议

#### 4.1. 设计优化

出现这个故障的原因是波特率使能一直按照周期发送,串口发送标志位信号与接收到的数据组帧发送指令的时刻有关,数据组帧发送指令的时序与波特率使能之间无固定关系,所以出现此种故障,所以修改波特率使能的发送模式,使其只在发送串口数据帧时发送,这样就避免了串口发送标志位与波特率使能同时为高[10]。

#### 4.2. 设计建议

在软件设计方面,串口发送状态机设计时应避免使用 有两个及以上无时序关系的信号同时控制状态机的状态 跳转,同时为了提高安全性,建议使用三段式状态机。

在工程实现方面,串行通信是航天电子产品中常用的通信形式,串口收发器也是FPGA中常见的设计单元,为了避免重复劳动,提高设计质量,建议将串口发送设计成一个可重用模块。

在系统测试方面,这次发生的故障在系统调试时出现, 在单机测试时未发现,而在系统联调时发现,因为两种试 验时的接收设备不同,所以在设计串口发送时也需关注实 际工作中输出接口连接设备的工作机制。

# 5. 结论

某星载设备在系统联调时发生了串口收发异常,经分析和判断问题出在使用FPGA的串口发送部分,对串口发

送的功能进行分解,找到这个异常的原因,即串口波特率使能信号的设计,经过计算出现故障的频率与实际频率基本相同。根据故障原因提出了设计优化的方法,经过试验和分析,此方法解决了串口发送异常的故障。同时根据这次排故工作,分别从软件设计、工程实现和系统测试方面三个方面提出了FPGA串口设计的一些建议,对工程应用具有借鉴意义。

# 参考文献

- [1] 颜世威,冯冲,施展.基于FPGA的多串口传输电路设计及验证[J].电子测试,2019,19(10):16-18。

- [2] 张诚, 孙列鹏, 肖薇等. 基于FPGA的串口实现[J]. 软件, 2018, 39(11): 219-223。

- [3] 刘杰, 臧炜, 梁晓鹏等. 一种新型的FPGA实现RS422串口通信方法[J]. 计算机测量与控制, 2017, 25 (3): 191-194。

- [4] 刘先博.基于FPGA与MCU的多串口通信接口设计与实现 [D].南京:南京理工大学,2014:32-36。

- [5] 孙毅.基于FPGA的智能串口设计与实现[D].西安: 西安电子 科技大学, 2011: 45-49。

- [6] 熊海军,王耀青.一种基于FPGA的多路串口控制器设计[J]. 测控技术,2013,32(9):137-143.

- [7] 袁志军.基于FPGA的高速率多串口扩展的设计与实现[D]. 哈尔滨: 哈尔滨工业大学, 2008: 25-26.

- [8] 潘松, 黄继业. EDA技术VHDL[M]. 北京: 清华大学出版社, 2006: 1-3.

- [9] 顾仁涛,王强.FPGA设计开发与工程实现[M].北京:北京邮电大学出版社,2013:1-15.

- [10] 吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2010: 156-159.